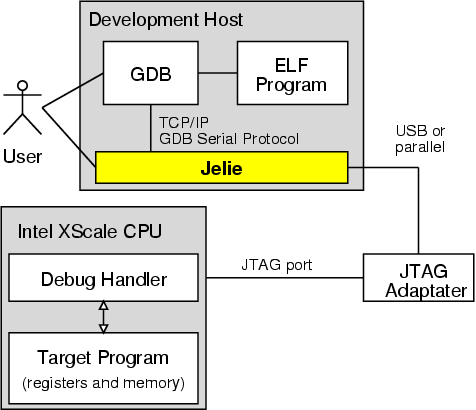

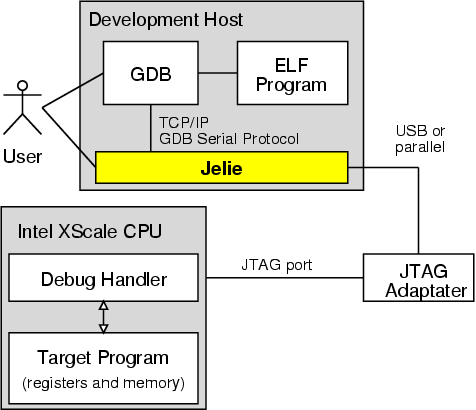

Jelie is a JTAG port driving software for Intel XScale CPU family. With only a JTAG connection, Jelie is able to upload a debug handler, initialize the memory, upload and debug programs.

Jelie can reach the JTAG port of the target processor trough a parallel port and a OCDemon McGraigor Wiggler adapter. USB connection using Anchor's EzUSB is also possible.

Jelie understands GDB's serial protocol on a TCP/IP port.

Jelie is released under the GNU General Public License (GPL).

Jelie runs on:

Jelie has been made for PXA250 and PXA255. We really do not know how it behaves with other XScale CPU.

The SDRAM controller is initialized by the debug handler of Jelie. It's hard

coded and there is absolutely no autodetection. Get a new configuration from

Intel web site. Read

debugHandler/webconf.S and make your new memory controller

configuration code look like it.

Remember that the debug handler is running from the instruction cache. You

can't access code in data mode. Instruction like:

ldr r0, =0xFF00FF00

will NOT work. Use instead the macro lreg, defined in

debugHandler/loadreg.S.

Jelie has been design for a precise board: Armonie. It's free hardware. Have a look at its web site.